Product Summary

Supports automatically load vendor ID and

product ID from EEPROM

Supports 4 GPIO pins

Optional EEPROM configuration

Very low power consumption mode:

Power reduced mode (cable detection)

Power down mode

Selectable TX drivers for 1:1 or 1.25:1

transformers for additional power reduction

Compatible with 3.3V and 5.0V tolerant I/O

100-pin LQFP with CMOS process

Parametrics

The DM9000 supports 8-bit, 16-bit and 32-

bit uP interfaces to internal memory accesses for different processors. The PHY of the DM9000 can

interface to the UTP3, 4, 5 in 10Base-T and UTP5 in

100Base-TX.

Features

Supports processor interface: byte/word/dword of

I/O command to internal memory data operation

■ Integrated 10/100M transceiver

■ Supports MII and reverses MII interface

■ Supports back pressure mode for half-duplex

mode flow control

■ IEEE802.3x flow control for full-duplex mode

■ Supports wakeup frame, link status change and

magic packet events for remote wake up

■ Integrated 4K dword SRAM

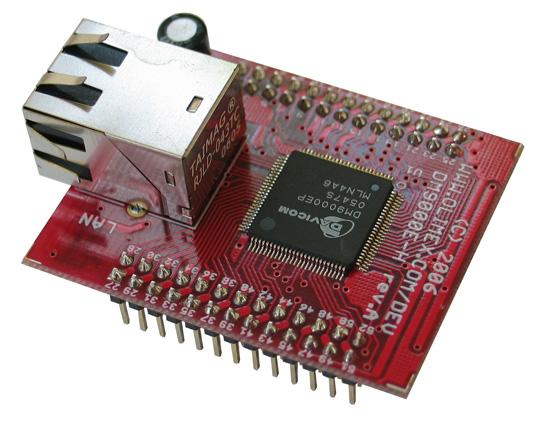

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

DM9000E-H |

Olimex Ltd. |

Ethernet Development Tools ETHERNET CONTROLLER HEADER BRD 50x40mm |

Data Sheet |

|

|

||||||

|

DM9000EP |

Other |

|

Data Sheet |

Negotiable |

|

||||||

(China (Mainland))

(China (Mainland))